## SECOND-HARMONIC REFLECTOR TYPE HIGH-GAIN FET FREQUENCY DOUBLER OPERATING IN K-BAND

Yoshitada Iyama, Akio Iida, Tadashi Takagi, Shuji Urasaki

Mitsubishi Electric Corporation

5-1-1 Ofuna, Kamakura-City,

Kanagawa Prefecture 247, Japan

## ABSTRACT

High gain FET frequency doubler with second harmonic reflector in input circuit has been developed. The reflector position which gives maximum multiplication gain depends on line loss. The relation between multiplication gain and the reflector position is varying with line loss.

K-band frequency doubler designed by this theory was fabricated. Good coincidence was obtained with high gain of 6dB.

## INTRODUCTION

A RF local source with excellent frequency stability and very low phase noise is required in communication fields. Such source is obtained by using multipliers and crystal oscillators. Though diodes or FETs are used for multipliers, FETs are more profitable because of high gain and suitability to MMICs(1). So we deal with a FET multiplier.

Rauscher gave the design method of the second harmonic reflector type FET frequency doubler(2). In this design method, transmission line is restricted to be lossless. But we found that the reflector position which gives the maximum multiplication gain depend on line loss. Here, we will present the design considerations and results for the FET doubler.

A K-band FET doubler which was designed by this theory has been fabricated. The multiplication gain of 6dB is obtained.

## DESIGN

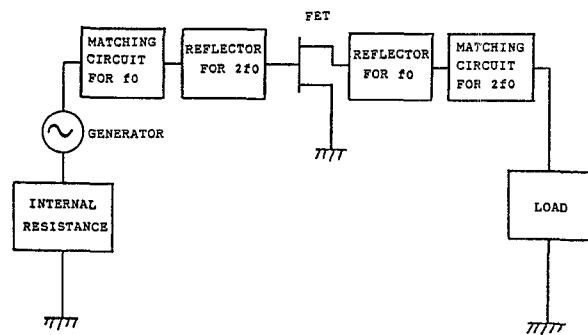

Fig.1 shows the block diagram of the second harmonic reflector type FET frequency doubler. The matching circuit for fundamental frequency( $f_0$ ) wave and the reflector for second harmonic( $2f_0$ ) wave are placed at the input, and the matching circuit for  $2f_0$  wave and the reflector for  $f_0$  wave at the output(3).

Fig.1 Block diagram of the second harmonic reflector type FET frequency doubler.

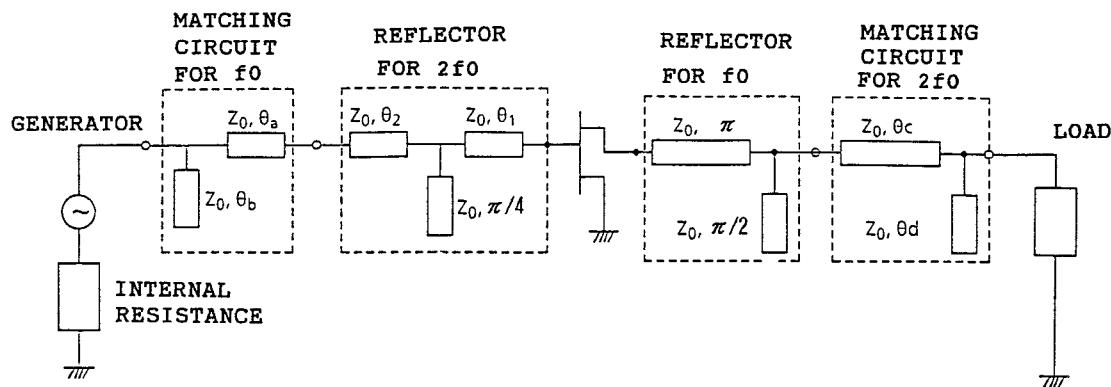

Fig.2 shows the equivalent circuit of the FET frequency doubler shown in Fig.1. The open circuited stub with the electrical length  $\pi/4$  is placed at electrical length  $\theta_1$  for  $f_0$  wave apart from the gate of the FET.

Second harmonic output power  $P_2$  in Fig.2 was calculated with harmonic balance method(4).

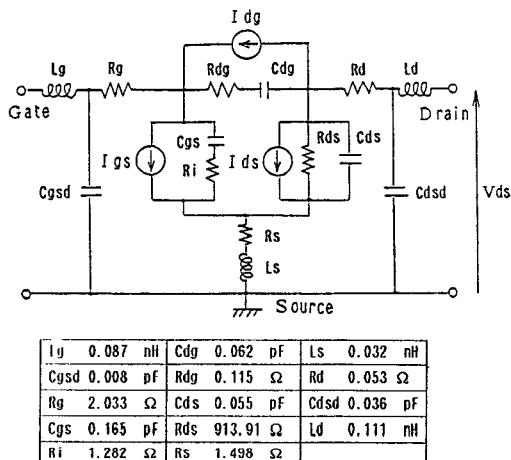

Parameters of the FET in Fig.2 are given in Fig.3.

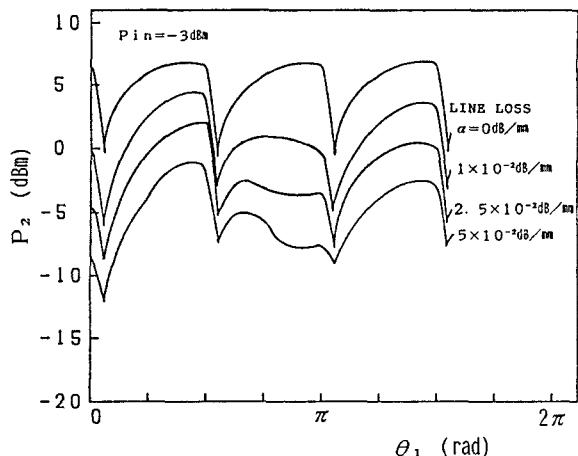

Fig.4 shows the  $P_2$  Vs.  $\theta_1$  characteristics with the line loss parameter  $\alpha$  at  $V_{gs}=-1V$  and  $V_{ds}=3V$ . In this case,  $f_0$  is 9.756Hz and the input power  $P_{in}$  is -3dBm.

Fig.2 Equivalent circuit of the reflector type FET frequency doubler.

(a)

(b)

Fig.3 (a) Equivalent circuit model and (b)  $I_{ds}$  vs.  $V_{ds}$  characteristics for the FET used in this calculation.

It is seen from Fig.4 that the output power  $P_2$  is dependent on  $\theta_1$  and  $\alpha$ . In the case of lossless line, maximum values of  $P_2$  appear periodically at the  $\pi/2$  interval of  $\theta_1$ , but in the lossy line, the lower maximum values of  $P_2$  appear periodically at interval  $\pi$  of  $\theta_1$ . According to computer simulation, gate voltage at lower maximum values of  $P_2$  is found to be very lower, and so the input circuit is considered to be the circuit at series resonance with low external  $Q$  for  $f_0$  wave, which is not observed in lossless line.

Fig.4 Calculated  $P_2$  vs.  $\theta_1$  characteristics as the line loss  $\alpha$  is parameter.

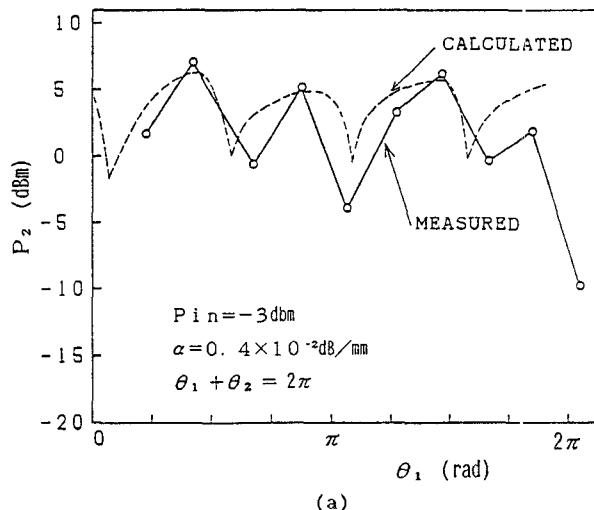

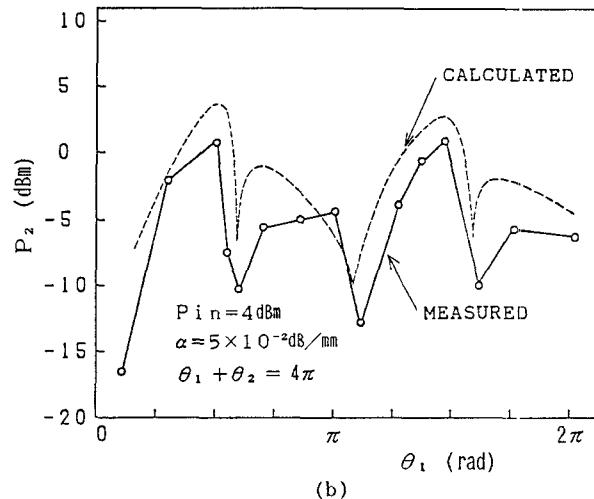

This theory was verified with experimental model. The results are shown in Fig.5(a), (b), with experimental values by solid line and calculated values by dotted line. Fig.5(a) is for low loss line ( $\alpha=0.4 \times 10^{-2} \text{ dB/mm}$ ), (b) for high loss line ( $\alpha=5 \times 10^{-2} \text{ dB/mm}$ ),  $f_0=9.75 \text{ GHz}$ . Good coincidence was obtained.

(a)

(b)

Fig.5  $P_2$  vs.  $\theta_1$  characteristics for

(a) low loss line, (b) high loss line.

#### FET DOUBLER MODULE

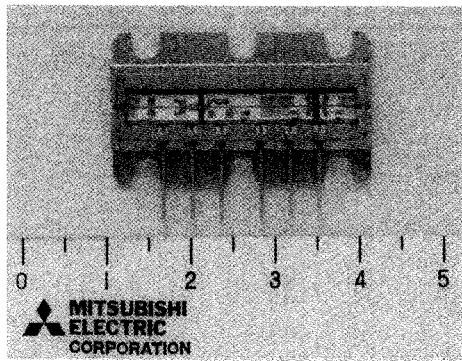

Fig.6 shows the photograph of the FET doubler module designed at 24GHz band. A FET doubler and a buffer amplifier are packaged in this module. For the miniaturization of the module, thin substrate is used, and so transmission line loss can not be neglected. Therefore, to obtain the maximum  $P_2$ , the reflector position of  $2f_0$  is determined by the above mentioned theory.

Fig.6 FET doubler module designed at 24GHz band.

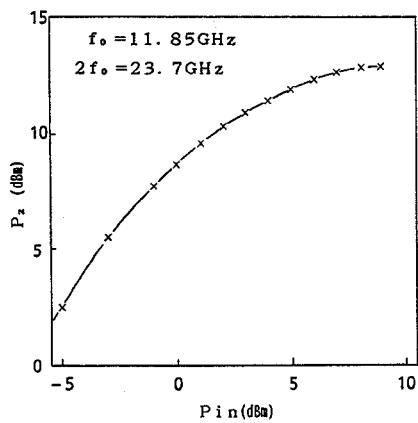

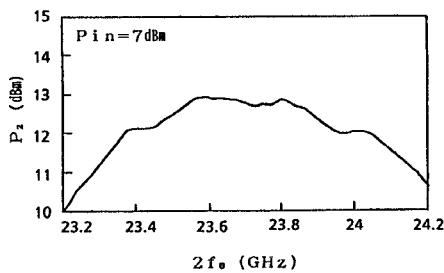

Fig.7 shows the  $P_2$  vs.  $P_{in}$  characteristics at the center frequency. The multiplication gain of the FET doubler 6dB is achieved when the input power is -3dBm. Fig.8 shows a frequency dependence of output power with 7dBm input power.

Fig.7 Pin vs. $P_2$  characteristics at the center frequency.

Fig.8 Frequency dependence of output power for +7dBm input.

## CONCLUSION

Second harmonic reflector type high gain FET frequency doubler operating at K-band which has been developed in Mitsubishi Electric Corporation was described. In the design, line loss was taken into consideration and the position of the second harmonic reflector was determined according to the theory. Multiplication gain 6dB was obtained with the fabricated module.

## REFERENCES

- (1) J.J.Pan, "Wideband MESFET Frequency Multiplier," 1978 IEEE MTT-S International Microwave Symposium Digest, pp.306-308, 1978.

- (2) C.Rauscher, "High-Frequency Doubler Operation of GaAs Field-Effect Transistors," IEEE Trans. Microwave Theory Tech., Vol. MTT-31, No. 6, pp. 462-473, 1983.

- (3) M.Akaike, "A Time-Domain Large-Signal Analysis of GaAs MESFET Devices Incorporating Frequency-Domain Expression for Termination Voltages," Proc. 18th European Microwave Conf., pp. 1175-1182, Sept. 1988.

- (4) A.Usida, et al, "Frequency-Domain Analysis of Nonlinear Circuits Driven by Multi-Tone Signals," IEEE Trans. Circuits Syst., Vol. CAS-31, No. 9, pp. 766-778, 1984.